# POWER MOSFET AVALANCHE DESIGN GUIDELINES

**Application Note**

# **TABLE OF CONTENTS**

| Table of Figures                               | 3  |

|------------------------------------------------|----|

| Introduction                                   | 4  |

| Overview                                       | 4  |

| Avalanche Mode Defined                         | 4  |

| Avalanche Occurrences In Industry Applications | 4  |

| Flyback Converter Example                      | 4  |

| Automotive Fuel Injector Coil Example          | 5  |

| Avalanche Failure Mode                         | 5  |

| Power MOSFET Device Physics                    | 5  |

| Rugged MOSFETs                                 | 6  |

| Avalanche Testing Details                      | 8  |

| Single Pulse Unclamped Inductive Switching     | 8  |

| Decoupled VDD Voltage Source                   | 9  |

| Avalanche Rating                               | 10 |

| E <sub>AS</sub> Thermal Limit Approach         | 10 |

| Single Pulse Example                           | 10 |

| Repetitive Pulse                               | 12 |

| Statistical Approach                           | 15 |

| Buyer Beware                                   | 16 |

| Conclusion                                     | 16 |

# **TABLE OF FIGURES**

| Figure 1  | Flyback Converter Circuit                                                                     | 4  |

|-----------|-----------------------------------------------------------------------------------------------|----|

| Figure 2  | Flyback Converter Switch Under Avalanche Waveform                                             | 4  |

| Figure 3  | Flyback Converter Switch Under Avalanche Waveform (Detail)                                    | 4  |

| Figure 4  | Automotive Injector Coil Circuit                                                              | 5  |

| Figure 5  | Automotive Injection Coil In Avalanche Waveforms                                              | 5  |

| Figure 6  | Power MOSFET Cross Section                                                                    | 5  |

| Figure 7  | Power MOSFET Circuit Model                                                                    | 5  |

| Figure 8  | Power MOSFET Cross Section Under Avalanche                                                    | 6  |

| Figure 9  | Basic HEXFET Structure                                                                        | 6  |

| Figure 10 | Power MOSFET Random Device Failure Spots                                                      | 7  |

| Figure 11 | Good Source Contact Vs. Bad Source Contact Illustration                                       | 7  |

| Figure 12 | I <sub>A</sub> at Failure vs. Test Temperature                                                | 8  |

| Figure 13 | Single Pulse Unclamped Inductive Switching Test Circuit                                       | 8  |

| Figure 14 | Single Pulse Unclamped Inductive Switching Test Circuit Output Waveforms                      | 9  |

| Figure 15 | Decoupled V <sub>DD</sub> Voltage Source Test Circuit Model                                   | 9  |

| Figure 16 | Decoupled V <sub>DD</sub> Voltage Source Test Circuit Waveforms                               | 9  |

| Figure 17 | Typical Simulated Avalanche Waveforms                                                         | 10 |

| Figure 18 | IRFP450 (500V Rated) Device Avalanche Waveforms                                               | 10 |

| Figure 19 | IRFP32N50K Data Sheet Excerptions                                                             | 11 |

| Figure 20 | Transient Thermal Impedance Plot, Junction to Case                                            | 11 |

| Figure 21 | Maximum Avalanche Energy Vs. Temperature for Various Drain Currents                           | 12 |

| Figure 22 | IRF7484 E <sub>AR</sub> Vs. T <sub>START</sub> for Various Duty Cycles, Single I <sub>D</sub> | 13 |

| Figure 23 | IRF7484 Typical Avalanche Current Vs. Pulsewidth for Various Duty Cycles                      | 13 |

| Figure 24 | IRF7484 Data Sheet Excerptions                                                                | 14 |

| Figure 25 | IRF7484 Typical Effective Transient Thermal Impedance, Junction-to-Ambient                    | 15 |

| Figure 26 | Avalanche Current Vs. Time for Various Inductor Values                                        | 15 |

| Figure 27 | Failure Energy Distribution                                                                   | 15 |

### INTRODUCTION

### Overview

International Rectifier has provided rugged Power MOSFET semiconductor devices for almost 20 years. To better understand and utilize IR HEXFET<sup>TM</sup> Power MOSFETs, it is important to explore the theory behind avalanche breakdown and to understand the design and rating of rugged MOSFETs. Several different avalanche ratings are explained and their usefulness and limitations in design is considered.

### **Avalanche Mode Defined**

All semiconductor devices are rated for a certain max reverse voltage ( $BV_{DSS}$  for Power MOSFETs). Operation above this threshold will cause high electric fields in reversed biased p-n junctions. Due to impact ionization, the high electric fields create electron-hole pairs that undergo a multiplication effect leading to increased current. The reverse current flow through the device causes high power dissipation, associated temperature rise, and potential device destruction.

# Avalanche Occurrences In Industry Applications

#### Flyback Converter Example

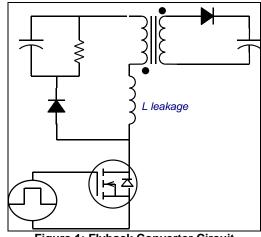

Some designers do not allow for avalanche operation; instead, a voltage derating is maintained between rated  $BV_{DSS}$  and  $V_{DD}$  (typically 90% or less). In such instances, however, it is not uncommon that greater than planned for voltage spikes can occur, so even the best designs may encounter an infrequent avalanche event. One such example, a flyback converter, is shown in Figures 1-3.

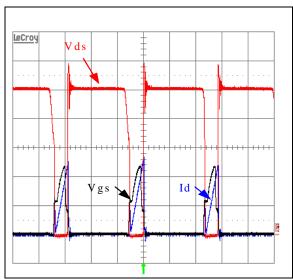

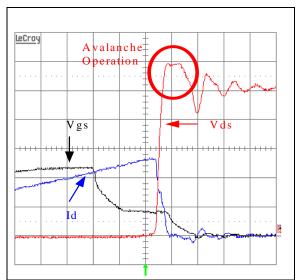

During MOSFET operation of the Flyback Converter, energy is stored in the leakage inductor. If the inductor is not properly clamped, during MOSFET turnoff the leakage inductance discharges through the primary switch and may cause avalanche operation as shown in the  $V_{DS}$ ,  $I_D$ , and  $V_{GS}$  versus time waveforms in Figures 2 and 3.

Figure 2: Flyback Converter Switch Under Avalanche Waveform

Figure 3: Flyback Converter Switch Under Avalanche Waveform (Detail)

#### <u>Note:</u> Red (V<sub>DS</sub>), Blue (I<sub>D</sub>), Black (V<sub>GS</sub>)

In this application, built in avalanche capability is an additional Power MOSFET feature and safeguards against unexpected voltage over-stresses that may occur at the limits of circuit operation.

Figure 1: Flyback Converter Circuit

### Automotive Fuel Injector Coil Example

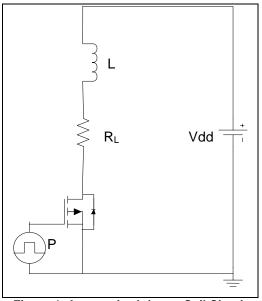

Other applications, such as automotive fuel injection, are designed to experience avalanche. See the example Injector Coil circuit below.

Figure 4: Automotive Injector Coil Circuit

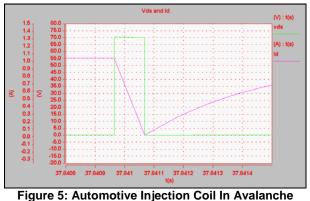

During switch operation, energy is stored in the solenoid inductance. Following switch turnoff, the inductor discharges on the primary switch causing avalanche operation as simulated in Figure 5.

-igure 5: Automotive Injection Coil In Avalanche Waveforms

In this application, avalanche tested and rated devices are a necessity for reliable circuit operation.

# AVALANCHE FAILURE MODE

Some power semiconductor devices are designed to withstand a certain amount of avalanche current for a limited time and can, therefore, be avalanche rated. Others will fail very quickly after the onset of avalanche. The difference in performance stems from particular device physics, design, and manufacturing.

### **Power MOSFET Device Physics**

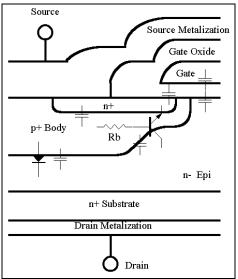

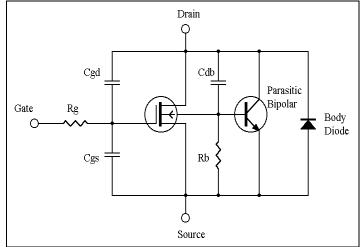

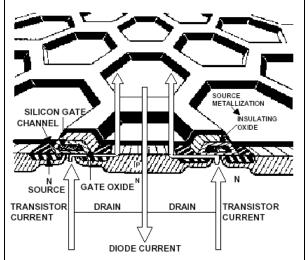

All semiconductor devices contain parasitic components intrinsic to the physical design of the device. In Power MOSFETs, these components include capacitors due to displaced charge in the junction between p and n regions, resistors associated with material resistivity, a body diode formed where the p+ body diffusion is made into the n- epi-layer, and an NPN (bi-polar junction transistor henceforth called BJT) sequence (BJT) formed where the n+ source contact is diffused. See Figure 6 for Power MOSFET cross section that incorporates the parasitic components listed above and Figure 7 for a complete circuit model of the device.

Figure 6: Power MOSFET Cross Section

Figure 7: Power MOSFET Circuit Model

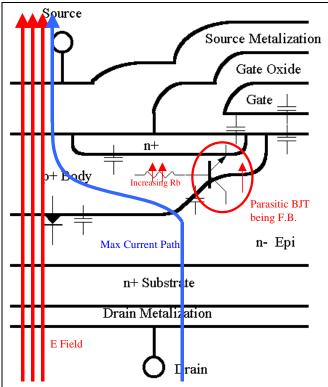

In avalanche, the p-n junction acting as a diode no longer blocks voltage. With higher applied voltage a critical field is reached where impact ionization tends to infinity and carrier concentration increases due to avalanche multiplication. Due to the radial field component, the electric field inside the device is most intense at the point where the junction bends. This strong electric field causes maximum current flow in close proximity to the parasitic BJT, as depicted in Figure 8 below. The power dissipation increases temperature, thus increasing since silicon resistivity increases with R<sub>B</sub>, From Ohm's Law we know that temperature. increasing resistance at constant current creates an increasing voltage drop across the resistor. When the voltage drop is sufficient to forward bias the parasitic BJT, it will turn on with potentially catastrophic results, as control of the switch is lost.

Figure 8: Power MOSFET Cross Section Under Avalanche

Typical modern Power MOSFETs have millions of identical trenches, cells or many strips in parallel to form one device, as shown in Figure 9. For Robust designs, then, avalanche current must be shared among many cells/strips evenly. Failure will then occur randomly in a single cell, at a high temperature. In weak designs, the voltage required to reach breakdown electric field is lower for one device region (group of cells) than for others, so critical temperature will be reached more easily causing the device to fail in one specific area.

Figure 9: Basic HEXFET Structure

### Rugged MOSFETs

First introduced in the middle 1980's, Avalanche Rugged MOSFETs are designed to avoid turning on the parasitic BJT until very high temperature and/or very high avalanche current occur. This is achieved by:

- Reducing the p+ region resistance with higher doping diffusion

- Optimizing cell/line layout to minimize the "length" of R<sub>B</sub>

The net effect is a reduction of  $R_B$ , and thus the voltage drop necessary to forward bias the parasitic BJT will occur at higher current and temperature.

Avalanche Rugged MOSFETs are designed to contain no single consistently weak spot, so avalanche occurs uniformly across the device surface until failure occurs randomly in the active area. Utilizing the parallel design of cells, avalanche current is shared among many cells and failure will occur at higher current than for designs with a single weak spot. A Power MOSFET which is well designed for ruggedness will only fail when the temperature substantially exceeds rated T<sub>JMAX</sub>.

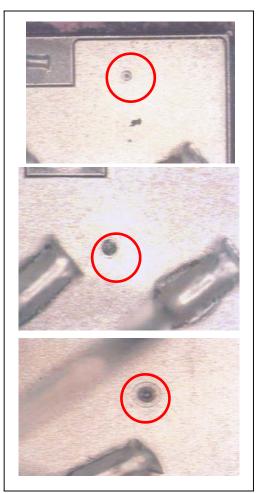

An analysis of various IR devices tested to destruction indicates that failure spots occur randomly in the active area. Some samples are shown in the Figure 10:

Figure 10: Power MOSFET Random Device Failure Spots

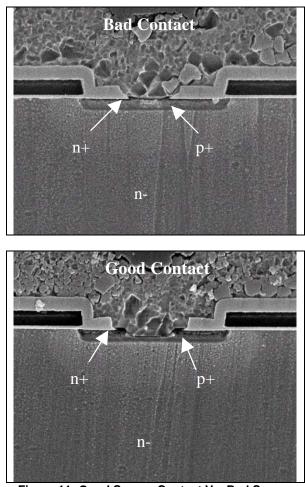

The risk of manufacturing process or fabrication induced "weak cell" parts is always present. The SEM cross-section micrograph on the top shows one such example. The Source metal contacts the n+ layer at the near surface, but not the p+ layer. As a result the BJT base is floating and easily triggerable. An example of a good contact is shown on the bottom. The source metal contacts and shorts the n+ layer to the p+ layer thus supressing the parasitic BJT operation.

Figure 11: Good Source Contact Vs. Bad Source Contact Illustration

Parts with weak cells such as are shown on the top of Figure 11 can be removed from the population by 100% avalanche ( $E_{AS}$ ) stress testing during production.

Through over 20 years of experience, International Rectifier has evolved design and manufacturing disciplines to validate power MOSFET design ruggedness of "E<sub>AS</sub> rated" devices. Presently IR uses a "three legged" approach during design:

1.) Statistically significant samples of prospective designs are tested to failure at test conditions chosen to reach extremes in temperature and current stress. Representative parts from DOE elements are tested to assure uniform avalanche failure across expected variation of critical process steps.

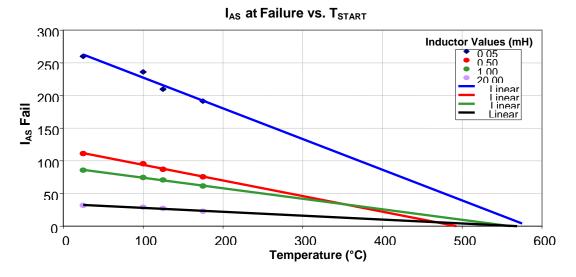

2.) Each design is tested to failure across Temperature and Inductor (time in avalanche) to assure that failure extrapolates to zero at a temperature well in excess of  $T_{JMAX}$ . (See sample Figure 12 of "I<sub>AS</sub> at failure vs. Tstart" below.) 3.) A sample of Final design parts are stressed with repetitive avalanche pulses of such a value to raise junction temperature to  $T_{JMAX}$ .

This "three legged" solution helps assure that designs are rugged and can be avalanche rated.

To summarize then: International Rectifier utilizes the following factors to provide rugged avalanche MOSFETs:

- Improved Device Design:

- to mute the parasitic BJT by reducing  $R_{\text{B}}$

- to eliminate the effect of weaker cells in particular positions of the

layout (i.e., cells along device termination, gate bussing, etc.)

- Improved Manufacturing Process:

- to guarantee more uniform cells

- to reduce incomplete or malformed cell occurrences

- Improved Device Characterization:

- to assure devices fail uniformly across wide range of I<sub>D</sub>, Temperature

- To assure device fails at very high (extrapolated) temperature

- To assure device is capable of surviving multiple avalanche cycles at the thermal limit

- 100% Avalanche Stress Testing

Figure 12: I<sub>AS</sub> at Failure Vs. Test Temperature

### **AVALANCHE TESTING DETAILS**

International Rectifier performs avalanche stress testing on its power semiconductor devices to assure conformance of new designs with avalanche rating, to validate parts for ruggedness, and to screen production for weak devices.

# Single Pulse Unclamped Inductive Switching

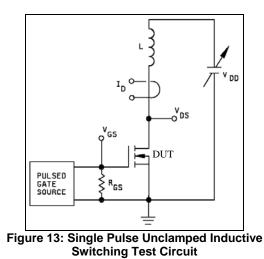

During the mid 1980's, IR initially used the single pulse unclamped inductive switching test circuit for avalanche testing that is shown below in Figures 13 and 14. This circuit is still referenced in older "legacy" product datasheets.

From the Figure 13 schematic we can calculate the single pulse avalanche energy  $(E_{AS})$  as:

$$E_{AS} = \frac{L \cdot I_{AS}^2}{2} \cdot \frac{VDS}{VDS - VDD}$$

(1)

The measured energy values depend on the avalanche breakdown voltage, which tends to vary during the discharge period due to the temperature increase. Also note that for low voltage devices  $V_{\text{DSS}}$ - $V_{\text{DD}}$  may become quite small, limiting the use of this circuit since it introduces high-test error.

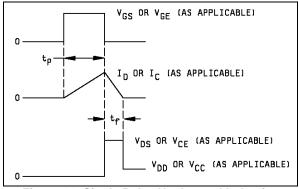

Figure 14: Single Pulse Unclamped Inductive Switching Test Circuit Output Waveforms

### **Decoupled VDD Voltage Source**

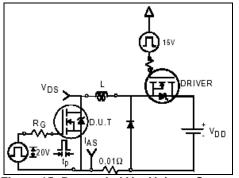

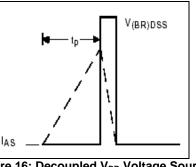

To surpass the limitations of the Single Pulse Unclamped Inductive Switching test circuit, International Rectifier started using the Decoupled  $V_{DD}$  Voltage Source illustrated in Figures 15 and 16 since the mid to late 1980's.

Figure 15: Decoupled V<sub>DD</sub> Voltage Source Test Circuit Model

Figure 16: Decoupled V<sub>DD</sub> Voltage Source Test Circuit Waveforms

Here a driver FET and recirculation diode are added so that the voltage drop across the inductor during avalanche is equal to the avalanche voltage. With this circuit (neglecting the angular  $E_{SR}$  in the inductor) the energy can be simply calculated as:

$$E_{AS} = \frac{1}{2}L \cdot I_{AS}^2 \tag{2}$$

A better and more accurate reading of the avalanche energy can be obtained by measuring instantaneous voltage and current in the device and integrating as described in the following equation:

$$E_{AS} = \int_{t_1}^{t_2} v_{(AV)DSS}(t) \cdot i_{AS}(t) \cdot dt$$

(3)

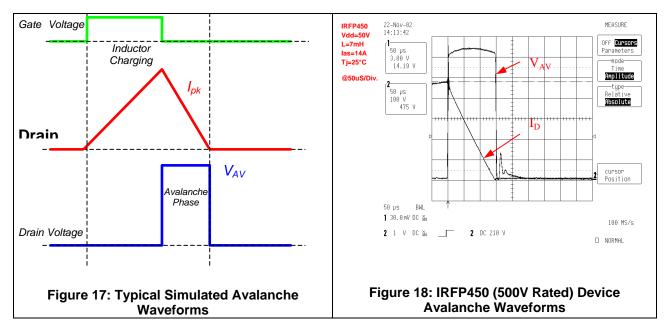

For further reference, Figures 17 and 18, depict ideal and actual avalanche waveforms, respectively.

Note that the peak avalanche voltage  $V_{AV}$  can be approximated as 1.3 times the device rating, or 650V. Further note that  $V_{(BR)DSS}$  and  $V_{AV}$  are used interchangeably in this text.

### **AVALANCHE RATING**

Generally, there are three approaches to avalanche rating devices:

- 1. **Thermal Limit Approach:** The device is rated to the value(s) of energy,  $E_{AS}$ , that causes an increase in junction temperature up to  $T_{JMAX}$ . International Rectifier  $E_{AS}$  avalanche rated MOSFETs are rated in this manner.

- 2. **Statistical Approach:** Devices are tested up to the failure point. The rating is given using statistical tools (e.g., Average  $(E_{AS}) 6\sigma$ ) applied to the failure distribution. Some IR parts are rated this way and indicated as  $E_{AS}$ (tested), generally in addition to the thermally limited rating. However, some MOSFET suppliers provide only this rating on their datasheets.

- 3. No rating at all.

While the first two approaches provide a value for avalanche energy, the designer must take care to know the important differences that are outlined below.

# **EAS THERMAL LIMIT APPROACH**

### Single Pulse

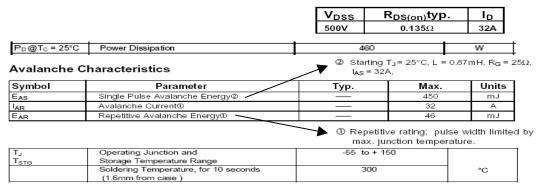

The single pulse avalanche rating ( $E_{AS}$ ) is based on the assumption that the device is rugged enough to sustain avalanche operation under a wide set of conditions subjection only to not exceeding the maximum allowed junction temperature. Typically, the avalanche rating on the data sheet is the value of the energy that increases the junction temperature from 25° C to  $T_{JMAX}$ , assuming a constant case temperature of 25° C and assuming a specified value of I<sub>D</sub> (usually set at 60% of I<sub>D</sub> (25° C). For example, consider the International Rectifier 500V 32 A device as excerpted from the datasheet below,

Figure 19: IRFP32N50K Data Sheet Excerptions

with the following initial conditions:

- Single Pulse Avalanche Current:  $I_{AS} = I_{D} = 32 \text{ A}$

- Starting Temperature:  $T_{START} = 25^{\circ}C$

- Inductor Value: L = 0.87 mH

To calculate the temperature increase due to the avalanche power dissipation we utilize a thermal model with Ohm's Law equivalence. The resulting equation follows:

$$\Delta T = Z_{TH} * P_{AV} \tag{4}$$

The average power dissipated during avalanche can be calculated as

$$P_{AV} = \frac{1}{2} \frac{V_{AV} \cdot I_{AS} \cdot t_{av}}{t_{av}} = 0.5 \cdot 650V \cdot 32A = 10kW$$

(5)

Avalanche voltage can be estimated as

$$V_{AV} \cong 1.3 \cdot BV_{DSS} = 1.3 \cdot 500V = 650V$$

(6)

Now from Equation 2 we can calculate

$$E_{AS} = \frac{1}{2}L \cdot I_{AS}^2 = 0.5 \cdot 0.87 mH \cdot 32^2 = 445 mJ$$

which agrees with the datasheet value within rounding of the least significant digit.

The duration of the avalanche power pulse can be calculated, assuming the inductor is discharging with a constant voltage applied to it, as

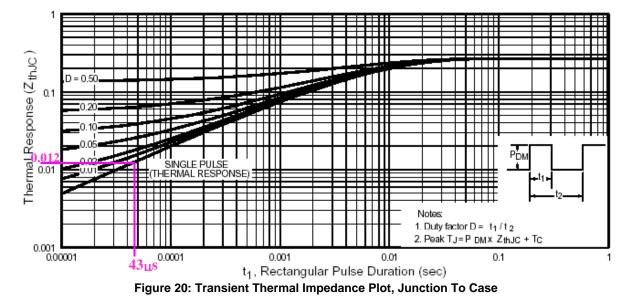

$$t_{av} \cong L \frac{I_{pk}}{V_{AV}} = 0.87 mH \cdot \frac{32A}{650V} \cong 43 \mu s$$

(7)

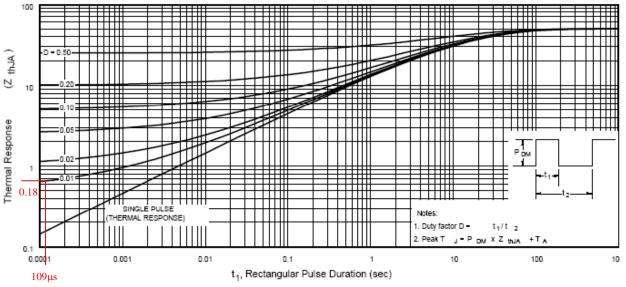

The thermal impedance  $(Z_{TH})$  for this pulsewidth can be read from the Transient Thermal Impedance Plot provided with the datasheet, as shown in Figure 20.

The temperature increase due to avalanche and the final junction temperature can therefore be calculated using Equation 4

$$\Delta T = Z_{TH} \cdot P_{AVG} = 0.012 \cdot 10kW = 120^{\circ}C$$

$$T_J = T_{start} + \Delta T = 145^{\circ}C \le T_{JMAX} = 150^{\circ}C$$

(8)

showing that the datasheet rating is consistent with the calculated  $T_{JMAX}$  within minor error due to reading  $Z_{TH}$  from Figure 20.

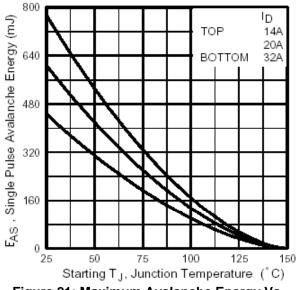

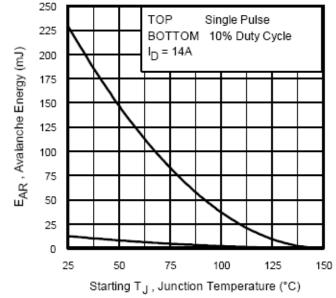

Figure 21: Maximum Avalanche Energy Vs. Temperature For Various Drain Currents

Figure 21 is included in datasheets for  $E_{AS}$  rated parts and shows many values of  $E_{AS}$  for varying starting  $T_J$  and  $I_D$ . Each point along the curves shown represents the energy necessary to raise the temperature to  $T_{JMAX}$ .

Note that this curve belies the myth of trying to compare datasheet table  $E_{AS}$  values : by varying current and/or temperature the  $E_{AS}$  value can vary by a range of 800x! Specifying  $E_{AS}$  at lower  $I_D$

values results in higher  $E_{AS}$  even though the device stress (T<sub>J</sub>) is the same.

### **Repetitive Pulse**

Historically, International Rectifier has rated the repetitive pulse avalanche energy ( $E_{AR}$ ) at 1/10000 of  $P_D$  (25°C). This practice is now supplanted on newer products by an explicit rating of avalanche operation up to the  $T_{JMAX}$  condition.

Datasheets utilizing this newer rating also include:

- E<sub>AS</sub>: the single pulse rating

- Z<sub>TH</sub> graph: Z<sub>TH</sub> vs. Time for various duty cycles (example in Figure 20 preceded by discussion)

- E<sub>AS</sub> graph: E<sub>AS</sub> vs. T<sub>start</sub> for various I<sub>D</sub> (example in Figure 21 followed by discussion)

- E<sub>AR</sub> graph: E<sub>AR</sub> vs. T<sub>start</sub> for various duty cycles, single I<sub>D</sub> (example and discussion to follows)

- I<sub>AR</sub> graph: Typical Avalanche Current vs. Pulsewidth for various duty cycles (example and discussion to follow below).

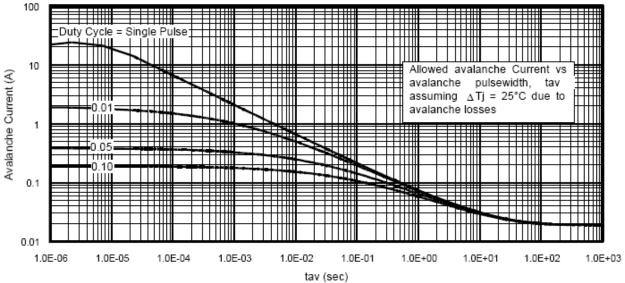

The E<sub>AR</sub> graph shows the avalanche energy necessary to raise the junction temperature from the starting temperature to  $T_{JMAX}$  for various duty cycles, at a given current. A sample EAR graph is given in Figure 22. The top curve represents single pulse behavior at 125A, while the bottom curve represents repetitive pulse operation at 125A, 10% In repetitive pulse operation, the duty cycle. junction temperature does not have sufficient time between pulses to return to the ambient level. The larger the duty cycle, the higher the junction temperature will be when the next pulse arrives. Therefore, with increasing duty cycle, the avalanche energy required to raise the junction temperature to T<sub>JMAX</sub> will be lower.

Figure 22: IRF7484 EAR VS. Tstart For Various Duty Cycles, Single ID

The IAR graph (see Figure 23) shows how the avalanche current varies with the avalanche pulsewidth for various duty cycles, with a "budgeted" increase in junction temperature due to avalanche losses assumed at  $(\Delta T) = 25^{\circ}C$ . An effect similar to that in the EAR graph occurs. In repetitive pulse operation, the junction temperature does not have sufficient time to decrease to the ambient temperature between pulses. As a result, the starting temperature for subsequent pulses will be higher than the ambient temperature. Therefore, smaller amount of avalanche а energy, corresponding to smaller avalanche current, will raise the junction temperature to  $T_{JMAX}$  for subsequent pulses. So for increasing duty cycles, the avalanche current required to raise the junction temperature by 25°C will decrease.

A detailed specific example now follows to illustrate how to design for repetitive avalanche operation. This example will utilize the Automotive Fuel Injection Coil circuit, shown earlier in Figure 4, with the 40V 14A IRF7484 MOSFET (Figure 24).

Figure 23: IRF7484 Typical Avalanche Current VS. Pulsewidth For Various Duty Cycles

| $V_{DSS}$ | $R_{DS(on)} \max (m\Omega)$ | I <sub>D</sub> |

|-----------|-----------------------------|----------------|

| 40V       | 10@V <sub>GS</sub> = 7.0V   | 14A            |

### Absolute Maximum Ratings

|                                  | Parameter                              | Max.         | Units |

|----------------------------------|----------------------------------------|--------------|-------|

| T <sub>J,</sub> T <sub>STG</sub> | Junction and Storage Temperature Range | -55 to + 150 | °C    |

#### Thermal Resistance

| Symbol           | Parameter              | Тур. | Max. | Units |

|------------------|------------------------|------|------|-------|

| R <sub>eJL</sub> | Junction-to-Drain Lead |      | 20   |       |

| R <sub>eJA</sub> | Junction-to-Ambient 3  |      | 50   | °C/W  |

### Electrical Characteristics @ T<sub>J</sub> = 25°C (unless otherwise specified)

|                     | Parameter                            | Min. | Тур. | Max. | Units | Conditions                                     |

|---------------------|--------------------------------------|------|------|------|-------|------------------------------------------------|

| R <sub>DS(on)</sub> | Static Drain-to-Source On-Resistance |      |      | 10   | mΩ    | V <sub>GS</sub> = 7.0V, I <sub>D</sub> = 14A ② |

Figure 24: IRF7484 Data Sheet Excerptions

The initial conditions are:

- Ambient Temperature: T<sub>a</sub> = 120°C

- Solenoid Inductance: L = 5mH

- Solenoid Resistance:  $R_L = 15\Omega$

- Pulse Frequency: f = 125Hz

- Supply Voltage: V<sub>DD</sub>= 14.5V

By applying Kirchoff's Laws to the Fuel Injection Coil circuit we find

$$V_{DD} = L \frac{di(t)}{di} + R_L i(t) + V_{AV} .$$

(9)

Using boundary condition at t = 0,  $i(t) = I_L = I_{AR}$ , yields the general solution in the time domain:

$$i(t) = I_{AR}e^{\left(-\frac{R_{L}}{L}t\right)} + \frac{V_{AV} - V_{DD}}{R_{L}}\left[e^{\left(-\frac{R_{L}}{L}t\right)} - 1\right].$$

(10)

Solving for the avalanche pulsewidth ( $t_{av}$ ) assuming  $i(t_{av}) = 0$  gives

$$t_{av} = \frac{L}{R_L} \ln \left[ 1 + \frac{I_{AR}R_L}{V_{AV} - V_{DD}} \right] = \frac{5mH}{15\Omega} \ln \left[ 1 + \frac{0.966A \cdot 15\Omega}{52V - 14.5V} \right] = 109\,\mu s$$

(11)

since avalanche voltage can be obtained from measurement (best), or estimated from the IRF7484 datasheet using Equation 6 as

$$V_{AV} \cong 1.3 \cdot BV_{DSS} = 1.3 \cdot 40V = 52V$$

,

and avalanche current can be calculated as

$$I_L = I_{AR} = \frac{V_{DD}}{R_L + R_{DS(on)}} = \frac{14.5V}{15\Omega + 10m\Omega} = 0.966A.$$

(12)

Repetitive avalanche energy can be calculated as

$$E_{AR} = \frac{I_{AR} \cdot V_{AV} \cdot t_{av}}{2} = \frac{0.966A \cdot 52V \cdot 109\mu s}{2} = 2.74 mJ$$

(13)

Average avalanche, and conduction power values can be calculated as

$$P_{AV} = \frac{E_{AR}}{t_{av}} = \frac{2.74mJ}{109\,\mu s} = 25.1W , \qquad (14)$$

$$P_{ave} = E_{AR} \cdot f = 2.74 mJ \cdot 125 Hz = 343 mW , \qquad (15)$$

$$P_{cond} = I_L^2 \cdot R_{DS(on)} \cdot D = (0.966A)^2 \cdot 10m\Omega \cdot 0.013 = 121\mu W$$

(16)

since the avalanche duty cycle can be calculated as

$$D = t_{av} \cdot f = 109\,\mu s \cdot 125 Hz = 0.013 \,. \tag{17}$$

The average junction temperature can be calculated as

$$T_{SS} = (P_{ave} + P_{cond})R_{\Theta} + T_a = (343mW + 121\mu W) \cdot 50 \,^{\circ}C_W + 120^{\circ}C = 137.2^{\circ}C$$

. (18)

The peak rise in junction temperature due to each avalanche pulse is given by

$$\Delta T = P_{AV} \cdot Z_{TH} = 25.1W \cdot 0.18^{\circ} C / W = 4.5^{\circ} C$$

(19)

where the thermal impedance  $(Z_{TH})$  is approximated from the Transient Thermal Impedance Plot provided with the datasheet, as shown in Figure 25.

Note that  $T_{SS}+\Delta T = 137.2+4.5 = 141.7C < T_{JMAX}$

# STATISTICAL APPROACH

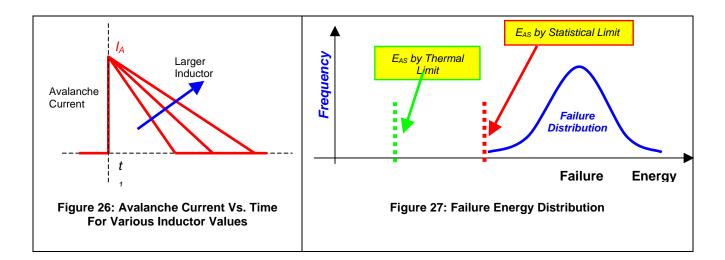

In this case, a sample of devices is tested for failure without limiting the maximum junction temperature to  $T_{JMAX}$ . The test consists of increasing the inductance value under a defined  $I_{AS}$  until each device fails. As shown in Figure 26, the energy, defined as the area under the  $I_{AS}$  curve, increases linearly with the load inductance value. Fixing L and increasing  $I_{AS}$  until failure occurs can accomplish a similar effect. The failure energy of each device is recorded and plotted

so that a failure distribution and  $E_{AS}$  value can be found, as shown below in Figure 27.

Note that the statistically determined  $E_{AS}$  value cannot be used to design for actual avalanche conditions. It represents operation at a single set of conditions that cannot be extrapolated to other circumstances without providing more information. Additionally, the conditions at which statistically rated  $E_{AS}$  values are given most often are outside the normal operation limits at which a part is qualified.

IR provides statistically based  $E_{AS}$  mostly in conjunction with the Thermally Limited values and to identify the product screening test numerical value. Other suppliers sometimes provide only a statistically based value.

Figure 25: IRF7484 Typical Effective Transient Thermal Impedance, Junction-to-Ambient

### **BUYER BEWARE**

Many suppliers rate power MOSFET avalanche capability with only a single number in the datasheet and without providing full circuit or test condition details. In such cases, buyer beware! It is not sufficient to merely compare the numeric values of avalanche energy which appear in datasheet tables. The following example will help illustrate one such pitfall.

Since avalanche energy depends on the inductor value and starting current, it is possible to have two pulses with the same energy but different shape provide two different junction temperatures. This phenomenon is illustrated in the following examples:

| Example 1                                              | Example 2                                              |

|--------------------------------------------------------|--------------------------------------------------------|

| Pulse:                                                 | Pulse:                                                 |

| $I_{AS} = 32A$                                         | $I_{AS} = 16A$                                         |

| L = 0.87 mH                                            | L = 3.48mH                                             |

| Result:                                                | Result:                                                |

| $E_{AS} = \frac{1}{2}L \cdot I_{AS}^2 = 445mJ$         | $E_{AS} = \frac{1}{2}L \cdot I_{AS}^2 = 445mJ$         |

| $t_{av} = L \frac{I_{pk}}{V_{(AV)DSS}} \cong 43 \mu s$ | $t_{av} = L \frac{I_{pk}}{V_{(AV)DSS}} \cong 86 \mu s$ |

| $Z_{TH} = 0.012^{\circ}C/W$                            | $Z_{TH} = 0.02^{\circ}C/W$                             |

| $\Delta T = 120^{\circ}C$                              | $\Delta T = 200^{\circ}C$                              |

| $T_J = 145^{\circ}C < T_{J\max}$                       | $T_J = 225^{\circ}C > T_{J\max}$                       |

Examples 1 and 2 both have the same energy, however, since the inductor varies, so does the junction temperature. While one junction temperature is within  $T_{JMAX}$ , the second is not.

Note as well that IR power MOSFETs which are " $E_{AS}$ " rated include graphs showing constant junction temperature energy values. See for example Figure 22, top curve. Which value of energy should be compared with another suppliers power MOSFET?

Another common industry practice is to rate avalanche capability based on curves showing allowable time in avalanche as a trade-off with drain current. At best, such curves are backed up with test to failure data as seen in Figure 12. However, sometimes these curves are based on statistically determined limits without apparent regard for junction temperature. The result is that a thermal  $T_J$  calculation (see examples 1 & 2) for the rated allowed condition may show that  $T_J$  exceeds  $T_{JMAX}$ , without reliability qualification data at this higher than  $T_{JMAX}$  condition. Again, buyer beware.

# CONCLUSION

With over 20 years of evolving experience, International Rectifier designs, characterizes, and rates Power MOSFETs to assure rugged and reliable operation while in avalanche. IR applies 3 different classes of avalanche rating:

- The Thermal Approach allows single pulse and (where indicated) repetitive pulse avalanche operation as long as neither  $I_{DMAX}$  nor rated  $T_{JMAX}$  are exceeded. Energy losses due to avalanche operation can be analyzed as any other source of power dissipation. Such thermally rated parts are indicated by IR with a rating of " $E_{AS}$ " and, more recently, with inclusion of repetitive avalanche SOA graph 9 (for example see Figures 22 & 23).

- Statistically based avalanche ratings are set based on sample failure statistics. At IR this rating is labeled " $E_{AS}$  (tested)" and corresponds to a production test screening limit. While the Statistical Approach generally gives higher energy value, it does not provide a practical method for evaluating avalanche capability in conditions that differ from the datasheet. Since circuit designers' conditions usually differ significantly, the Statistical Approach does not give a clear idea on how to design for occurrence of avalanche.

-Some legacy products were designed by IR without an avalanche rating. Devices without an avalanche rating on the datasheet should not be used In circuits which will see avalanche condition during any mode of operation. By special arrangement, most such designs can be avalanche guaranteed; contact factory representative for further information. Power MOSFET users should take care to understand differences in avalanche rating conditions between various suppliers. Devices that are not "avalanche Robust" can cause unexpected and seemingly unexplained circuit failure. Some manufacturers do not rate their MOSFETs for avalanche at all. Others use a statistical rating alone which does not offer the same assurance for robust operation provided by a more complete characterization and rating such as IR uses for "E<sub>AS</sub> rated" devices. In this regard, "the devil is in the details"; merely contrasting values of avalanche energy that appear in datasheets tables is not an accurate metric of device ruggedness.